- INDIRECTION REDIRECTION MEMORY SOFTWARE

- INDIRECTION REDIRECTION MEMORY CODE

- INDIRECTION REDIRECTION MEMORY PLUS

Two 3-bit "Extend Memory Registers", called EM2 and EM3, are provided which can be loaded with a value to be used as the high-order three bits of the effective address. The 930 offers a "memory extension system" that allows addressing more than 16284 words.

The 920 can have up to 1024 priority interrupts. The fixed-point add time is the same as the 910 (16 μs), but the fixed-point multiply is roughly twice as fast at 128 μs. Main memory on the 920 is 4096 to 16384 words of magnetic core memory. The SDS 910 weighed about 900 pounds (410 kg).

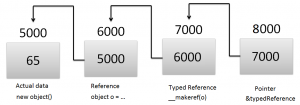

(indexing preceding indirecting), potentially recursively.

INDIRECTION REDIRECTION MEMORY CODE

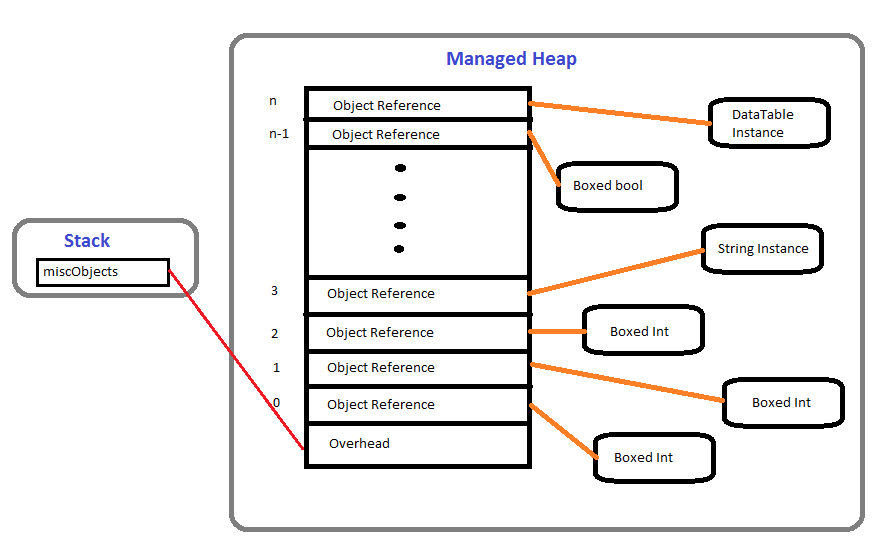

The instruction format for the 910 and 920 systems is as follows:īit 1 '1'b indicates that the operand address is to be indexed.īit 2 '1'b indicates that this instructionīits 3-8 is the instruction code or programmed-operator id.īit 9 '1'b indicates that the operand address shall be indirected Two hardware interrupts are standard with up to 896 more optional. A fixed-point add instruction takes 16 μs, a fixed-point multiply takes 248 μs. Main memory on the 910 is 2048 to 16384 words of magnetic-core memory with a cycle time of 8 μs. Bit 9 of location zero is set to '1'b to indicate an indirect address, allowing the programmed operator routine to indirectly access the data specified in the address of the POP instruction. Bit zero of location zero is set to the current value of the overflow indicator and the indicator is reset. The location of the POP instruction is saved in location zero. If the P bit is set, an instruction code of xx is treated as a call to location 1xx (octal). The six bit instruction code allows up to 64 programmed operators (octal 00 through 77). The programmed operator facility allows the instruction code field to indicate a call to a vector of subroutine addresses. Multiple levels of indirect addressing are allowed. The word at the effective indirect address is decoded as if it were an instruction (except that the instruction code is ignored), allowing an indirect address to also specify indirection or indexing. The format is the same as double precision except that only 24 bits of fraction are used.įor address generation, indexing, if specified, is performed before indirection. | frac(cont) |±|exponent | low-order word The value of the number is F*2 E, where F is the fraction and E is the exponent.

The binary point is assumed to be immediately left of the high-order bit of the fraction. Both the exponent and the fraction are stored in big-endian twos-complement format.

Single precision has a 24-bit signed fraction and a 9-bit signed exponent, double precision has a 39-bit fraction and a 9-bit exponent. All floating point numbers are stored as 48-bit double words.

INDIRECTION REDIRECTION MEMORY SOFTWARE

Maximum address space is 2 14 or 16,384 words (16 KW-64 K char) on the 910 and 9, 930, and 940 support up to 32K (128 K char), although the method of accessing additional memory varies.įixed point data is 24-bits, two's complement, big-endian.įloating point is implemented in software using "programmed operators", except on the SDS 9300 which has hardware floating point. The W and Y registers are used for input/output. The 9300 has three index registers X1 through X3 which can be used as base registers to allow access to memory above 16K words.

INDIRECTION REDIRECTION MEMORY PLUS

Programmer-accessible registers are A (accumulator), B (extension), X (index), and P (program counter-14 bits), plus an overflow indicator. All systems are 24-bit single address machines.

0 kommentar(er)

0 kommentar(er)